#### BULETINUL INSTITUTULUI POLITEHNIC DIN IAȘI Publicat de Universitatea Tehnică "Gheorghe Asachi" din Iași Tomul LIX (LXIII), Fasc. 4, 2013 Secția ELECTROTEHNICĂ. ENERGETICĂ. ELECTRONICĂ

# MODELLING AND SYNTHEZIS OF REAL-TIME CONTROL SYSTEMS BASED ON HARDWARE TIMED PETRI NETS

BY

# VIORICA SUDACEVSCHI\* and VICTOR ABABII

Technical University, Kishinew, Moldova

Received: November 4, 2013

Accepted for publication: December 14, 2013

**Abstract.** This paper presents a synthesis method of real-time control systems based on direct mapping of Petri net model into Field Programmable Gate Array (FPGA) circuit. Synchronous timed Petri nets have been developed to specify and model the control system. Switching to hardware description of the system is achieved through Hard Timed Petri Nets (HTPN). Direct correspondence between the elements of the original specification and circuit components ensures that the behavioral properties and time constraints, under which activate the control system, will be respected.

**Key words:** timed Petri nets; Timed Hard Petri Nets; real-time control system; FPGA.

#### 1. Introduction

The advantages of reconfigurable devices, including FPGAs (Field Programmable Gate Arrays), make them very popular during the last years. FPGAs and reconfigurable computing accelerate a lot of applications (Bondalapti *et al.*, 2002; Buell *et al.*, 2007; El-Ghazawi *et al.*, 2008; Todman *et al.*, 2005). One of the most perspective directions is the use of FPGA circuits for control systems design. The interest in this approach is based on the ability to run in parallel several control strategies and the possibility of real-time reconfiguration of the control system at the hardware-level.

.

<sup>\*</sup>Corresponding author: e-mail: svm700@mail.ru

One of the problems in the design of real-time control systems is the proper synchronization of all processes. Certain operations are running at predetermined time limits and processing involves time constraints. To ensure an efficient messages and data exchange is necessary to generate status and synchronization signals in strict accordance with time. In these cases, time is the basic value and time constraints require a very high accuracy that can be achieved only by using parallel or concurrent data processing techniques (Baer, 2010).

Implementation of parallel data processing algorithms (Cristea, 2002) requires the verification for correctness of operation and eventual conflicts, which may lead to serious errors. For this purpose modern methods and techniques based on timed Petri nets models (Cassez *et al.*, 2006; Lime *et al.*, 2006) can be used.

Classical methods of real-time control systems design based on logic synthesis presents a number of disadvantages, namely high computational complexity, system specification only at low abstraction levels, resulting circuit structure does not match to the behavioral model structure. Direct mapping techniques excludes these disadvantages, which are particularly important for real-time systems in which the operations are executed according to time constraints.

In the present paper is proposed a synthesis method of real-time control systems based on direct mapping of Petri Net model into the hardware architecture. For this purpose an extension of Petri Nets – Timed Synchronous Petri Nets (TSPN) was developed. A model for direct implementation into FPGA circuit was proposed, namely Hard Timed Petri nets (HTPN). Direct correspondence between the elements of the original specification and circuit components ensure that time constraints will be respected.

## 2. Timed Synchronous Petri nets (TSPN)

A Timed Synchronous Petri Net (TSPN) is a 7-tuple  $(P, T, A, M_0, M_{\text{max}}, C, \theta)$ , where:

$P = \{p_1, p_2, ..., p_N\}$  is a finite and non-empty set of places;

$T = \{t_1, t_2, ..., t_L\}$  is a finite and non-empty set of *transitions*;

$A \subseteq (P \times T) \cup (T \times P)$  is a set of *arcs*.

The set of arcs consists of three subsets:  $A = A^N \cup A^I \cup A^T$ ,  $A^N \cap A^I \cap A^T = \{\emptyset\}$ ,  $A^N$  – normal arcs,  $A^I$  – inhibition arcs,  $A^T$  – test arcs;

$M_0 = \left\{ M_0^{P_1}, M_0^{P_2}, \dots, M_0^{P_N} \right\}$  is the *initial marking*, defined as an initial number of tokens in each place;

$M_{\text{max}} = \left\{ M_{\text{max}}^{P_1}, M_{\text{max}}^{P_2}, \dots, M_{\text{max}}^{P_N} \right\}$  is the *maximal marking*, defined as a maximal number of tokens in each place;

C is the *synchronization variable* that enable the transitions firing (Peterson, 1981);

$\theta = \left\{ \tau_j, \forall j = \overline{1, L} \right\}$  is the set of time values that specify the delays of transitions firing.

Subset  $A^N$  defines the normal arcs, through which tokens are removed from each input place and are added to each output place. Subsets  $A^I$  and  $A^T$  are necessary in behavioral analysis but do not remove or add tokens.

The weight of each arc is equal to one. Sets P and T are disjoint,  $P \cap T = \{\emptyset\}$ , and satisfy the condition,  $P \cup T \neq \{\emptyset\}$ .

A transition,  $t_j$ , is enabled by the current marking,  $M_k$ , noted  $M_k[t_j>$ , if and only if the relation

$$V(t_{i}, M_{k}) = V_{\Delta^{N}}(t_{i}, M_{k})V_{\Delta^{I}}(t_{i}, M_{k})V_{\Delta^{T}}(t_{i}, M_{k})C\Delta,$$

is true, where:

$$V_{A^N}(t_j, M_k) = \prod_{\forall p_i \in {}^*t_i} (M_k^{p_i} \ge 1)$$

is the enabling condition in case of presence of at least one token in all input places, connected with  $t_j$  through normal arcs ( $M_k^{p_i}$  – current marking in place  $p_i$ ,  $t_j$  – input places for transition  $t_j$ ). For  $A^N = \emptyset$  is considered  $V_{A^N}(t_j, M_k) = 1$ ;

$$V_{A^{l}}(t_{j}, M_{k}) = \prod_{\forall p_{i} \in {}^{*}t_{j}} (M_{k}^{p_{i}} = 0)$$

is the enabling condition in case of absence of tokens in all input places, connected to  $t_j$  through inhibition arcs. For  $A^I = \emptyset$  is considered that  $V_{A^I}(t_j, M_k) = 1$ ;

$$V_{A^{T}}(t_{j}, M_{k}) = \prod_{\forall p_{i} \in {}^{*}t_{j}} (M_{k}^{p_{i}} \geq 1)$$

is the enabling condition in case of presence of at least one token in all input places, connected to  $t_j$  through test arcs. For  $A^T = \emptyset$  is considered  $V_{A^T}(t_j, M_k) = 1$ .

The firing of enabled transitions,  $T(M_k)$ , will produce a new marking,  $M_{k+1}$ , according to the following rule:

$$\forall p_{i} \in {^{*}T(M_{k})}[M_{k+1} = M_{k} - 1], (i = \overline{1, N}),$$

$$\forall p_{i} \in T^{*}(M_{k})[M_{k+1} = M_{k} + 1], (i = \overline{1, N}),$$

(1)

where:  ${}^*T(M_k)$  is the set of all input places for transitions from  $T(M_k)$ ;  $T^*(M_k)$  is the set of all output places for transitions from  $T(M_k)$ ;  $M_{k+1}$  and  $M_k$  are the number of

tokens in place p after and before the transitions firing from  $T(M_k)$  (Sudacevschi, 2009).

Petri nets allow the expression of parallel or concurrent activities in terms of transitions. Two enabled transitions in a Petri net model are concurrent if they are in causal independent relationship (they are not in conflict with each other) and therefore can fire in parallel. The level of concurrent activity in a Petri net depends on the number of enabled transition for any reachable marking,  $M_k$ . Since in TSPN is possible a simultaneous firing of all enabled transitions, the level of concurrent activity will be determined by the number of fired transitions.

## 3. Hard Timed Petri Nets (HTPN)

A Hard Timed Petri net (HTPN) is a 13-tuple:  $\text{RPH} = \left\langle T, P, A^+, A^-, A^S, A^T, A^I, P^{\text{In}}, P^{\text{Out}}, M_0, M_{\text{max}}, C, D \right\rangle, \text{ where:}$

$T = \{t_1, t_2, ..., t_L\}, T \neq \emptyset$ , is a set of processing elements that correspond to transition nodes;

$P = \{p_1, p_2, ..., p_N\}, P \neq \emptyset$ , is a set of processing elements that correspond to place nodes;

$A^{+}$  is a set of increment connections of the number of tokens in position processing element  $p_{i}$ ;

$A^-$  is a set of decrement connections of the number of tokens in position processing element  $p_i$ ;

$A^S$  is a set of state connections that determine the enable firing condition of the transition  $t_i$  related to the marking in the input place,  $p_i$ ;

$A^T$  is a set of test connections, which has the same function as the set of state connections, but the transition firing does not change the marking in the input place;

$A^{I}$  is a set of inhibitor connections, which provides an enabling function, when the place  $p_{i}$  stores no tokens. Inhibitor connection has the ability to test whether a place is empty. The firing does not change the marking in the input place;

$P^{\text{In}} = \left\{ P_i^{\text{In}}, i = \overline{1, N^{\text{In}}} \right\}, P^{\text{In}} \in P$ , is a set of places that specify the input signals to the digital system;

$P^{\text{Out}} = \left\{ P_i^{\text{Out}}, i = \overline{1, N^{\text{Out}}} \right\}, P^{\text{Out}} \in P$ , is a set of places that specify the output signals from the digital system;

$M_0 = \{M_0^{P_1}, M_0^{P_2}, \dots, M_0^{P_N}\}$  is the initial marking, defined as the initial number of tokens in each place;

$M_{\text{max}} = \{M_{\text{max}}^{P_1}, M_{\text{max}}^{P_2}, ..., M_{\text{max}}^{P_N}\}$  is the maximal marking, defined by

the maximal number of tokens in each place;

C is the synchronization variable;

D is a set of processing elements, called "Delay", which specify delays between transitions enabling and firing according to time values,  $\theta$ .

The modeling and design of control systems are based on HTPN models. To make possible the direct mapping of these models into hardware circuit were developed the following processing elements: Position (P), Transition (T) and Delay (D) (Sudacevschi, 2006).

## 4. Modeling and Implementation of a Control System

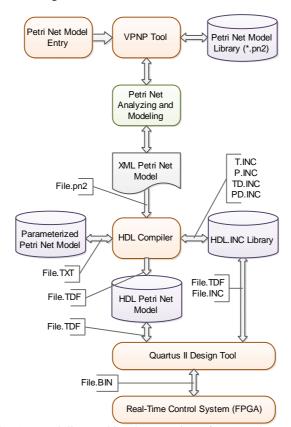

The sequence of operations for modeling and implementation of a control system based on HTPN models is presented in Fig. 1. The diagram includes three basic components: VPNP Tool – software tool for modeling and validation of Timed Petri Net Models, HDL Compiler – software tool for converting a Petri Net Model from XML to HDL format, Quartus II Design Tool – software tool for HDL compilation, functional simulation of the control system and FPGA configuration (Altera, 2013).

Fig. 1 – Modeling and implementation of a control system.

#### 4.1. Control System Synthesis

S t e p 1. Petri Net Model is drawn as a set of graphical symbols of objects *P*, *T*, *A* and the connectivity between them using an object design entry environment of VPNP Tool (Petri Net Model Entry). The introduced Petri Net Model is stored in XML format with extension \*.pn2 (Petri Net Model Library). In order to verify the behavioral correctness of the Petri Net Model, modeling and functional verification methods are applied. The resulted information is presented in XML format in File.pn2 (XML Petri Net Model) that is used in next step.

S t e p 2. HDL Compiler analyses XML file that contains Petri Net Model and extracts information necessary for HDL compilation. The extracted parameters (Parameterized Petri Net Model) is saved in File.txt. For HDL synthesis of a non-timed subnet functional objects P.INC and T.INC are used, for HDL synthesis of a timed subnet – TD.INS and PD.INC, respectively. The resulted HDL Petri Net Model is contained in File.TDF (HDL Petri Net Model).

S t e p 3. HDL Petri Net Model contained in File.TDF is imported into Quartus II Design Tool. After compilation time diagrams and statistics information are generated. The resulted File.bin is used to configure the FPGA circuit.

# **5. Control System Structure**

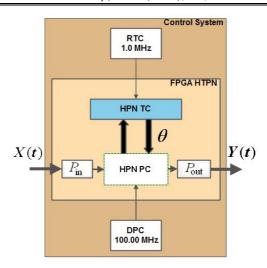

The block diagram of a control system implemented using HTPN is presented in Fig. 2. The block diagram includes: RTC (Real Time Clock) 1.0 MHz – time controller for generation of synchronization signals. In order to optimize the control system complexity, RTC generator frequency is selected as the lowest divider for all delays in the control system; DPC (Data Processing Clock) 100 MHz – clock generator for data processing synchronization with 100.00 MHz frequency (can be replaced by maximum operating frequency of FPGA circuit); FPGA HTPN – FPGA circuit for Hard Timed Petri Net implementation; X(t) Pin – control system input logic signals that determine the state of the controlled process; Y(t) Pout – control signals; HPN TC – Hard Petri Net to generate time values  $\theta$  associated with transitions; HPN PC – Hard Petri Net for X(t) processing and Y(t) generation;  $\theta = \left\{\tau_j, \forall j = \overline{1,L}\right\}$  – the set of time values specifying transitions firing delays.

The mathematical model of a control system is C = [X(t), Y(t), HTPN], where:

$X(t) = \left\{x_i(t), \forall i = \overline{1, N}\right\}$  is a set of input logic signals;

$Y(t) = \{y_i(t), \forall i = \overline{1, M}\}$  is a set of control logic signals;

HTPN – Hard Timed Petri Net that is implemented into FPGA circuit.

Fig. 2 – Control system block diagram.

# 6. Real-Time Model of a Process

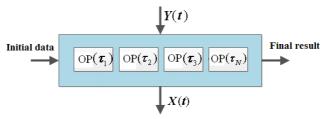

Let's consider a real-time process (RTP) in which for execution of each operation a timeframe is assigned. RTP consists of a set of concurrent or parallel operations, OP,

$$RTP = \bigcup_{i=1}^{N} (OP(\tau_i)).$$

(2)

The structure of the real-time process is presented in Fig. 3, where Initial data - input data to the digital system or raw materials required for the production process, *Final result* – the result of the data processing or the final product obtained after technological/production process completion, X(t) – the logic state of operations  $OP_i$ ,  $\forall i = \overline{1, N}$  and Y(t) – control signals for operations fulfillment.

Fig. 3 – Real-time process structure.

This structure can be applied to the design of concurrent data processing systems and the design of technological/production processes.

The logical behavior of a real-time process can be described by the following model:

$$\begin{aligned} & \text{OP}_1: \text{IF}(x_1), \text{init} \left(y_1\right), \\ & \text{Delay}(\tau_1), \text{set/reset} \left(y_1\right), \\ & \dots \\ & \text{OP}_i: \text{IF}(x_i), \text{Delay}(\tau_i), \text{set/reset} \left(y_2\right), \\ & \text{Delay}(\tau_{i+1}), \text{reset/set} \left(y_i\right), \\ & \dots \\ & \text{OP}_N: \text{IF}(x_N), \text{Delay}(\tau_m), \text{set/reset} \left(y_N\right), \end{aligned} \end{aligned}$$

where: IF( $x_i$ ),  $\forall i = \overline{1,N}$  — the condition for timeframe  $\tau_j$  calculation; Delay( $\tau_j$ ) — delays of the enabled transition firing; set/reset( $y_i$ ) — set or reset of the control signal after a timeframe,  $\tau_j$ . In case of complex processes one control signal,  $y_i$ , can have more then one timeframe,  $\{\tau_j, \tau_{j+1}, \ldots\}$ , that synchronizes control signal transition from one state to another.

# 7. Example of a Control System Synthesis

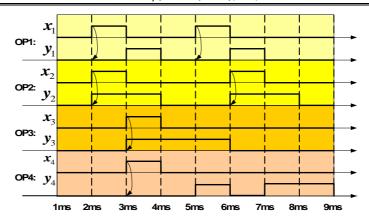

Let's have an RTP that contains four parallel operations, described by the following model:

$$RTP = \begin{cases} OP_1 : IF(x_1 = 1), \ y_1 = 0, Delay(1 \text{ ms}), \\ y_1 = 1, Delay(1 \text{ ms}), \ y_1 = 0; \\ OP_2 : IF(x_2 = 1), \ y_2 = 1, \\ Delay(2 \text{ ms}), \ y_2 = 0; \\ OP_3 : IF(x_3 = 1), \ y_3 = 1, \\ Delay(3 \text{ ms}), \ y_3 = 0; \\ OP_4 : IF(x_4 = 1), Delay(2 \text{ ms}), \\ y_4 = 1, Delay(1 \text{ ms}), \ y_4 = 0, \\ Delay(1 \text{ ms}), \ y_4 = 1, \\ Delay(2 \text{ ms}), \ y_4 = 0. \end{cases}$$

$$(4)$$

Model (4) has the time diagram represented in Fig. 4.

Control signals for operations  $OP_1$ ,  $OP_2$ ,  $OP_3$  have only one timeframe; control signal for operation  $OP_4$  has two timeframes. This fact proves the ability of HTPN to generate complex control signal with programmed length.

Fig. 4 – Time diagram of model (4).

The HTPN for control system of the process defined by model (4) is represented in Fig. 5.

Fig. 5 – HTPN for model (4).

HTPN consists of two subnets: HPN TC – for generation of timeframes  $\theta = \{1, 1, 2, 3, 2, 1, 1, 2\}$  ms and HPN PC – for control signals  $Y = \{y_1, y_2, y_3, y_4\}$  generation according to input signals  $X = \{x_1, x_2, x_3, x_4\}$ .

The specification of the HTPN components:  $x_1,...,x_4$  – input variables to the control system;  $y_1,...,y_4$  – control variables; RTC – synchronization signal for timeframes  $\theta = \{1,1,2,3,2,1,1,2\}$  ms generation (a common 1 ms divider can be defined for timeframes, it will determines the 1.0 kHz generator frequency); t1, t2, t3, t4, t14, t16, t18, t20 – transitions for synchronization of timeframes generation; Delay( $\tau_i$ ) – places for clock pulses counting necessary for timeframes generation; D1,...,D7 – intermediate places for control signals generation; t5, t6, t7, t8, t9, t10, t11, t12, t13, t17, t19, t21 – transitions for control signals generation.

## 8. Conclusions

In this paper an approach for real-time control systems synthesis based on Petri nets models has been presented. For behavioral specification and modeling of a control system, Timed Synchronous Petri Nets (TSPN) has been developed. TSPN is used to analyse functional properties of the designed control system and time constraints. Hard Timed Petri Nets (HTPN) was proposed to perform the conversion of the model to logic circuit. HTPN consists of functional elements and logical connections between them. The direct implementation of the HTPN model into FPGA circuit ensures that the behavioral properties and time constraints, under which activate the control system, will be respected. In order to validate the proposed method an example of control system synthesis has been presented.

#### REFERENCES

- Baer J.L., *Microprocessor Architecture, from Simple Pipelines to Chip Multiprocessors*. Cambridge Univ. Press, UK, 2010.

- Bondalapti K., Prasanna V., Reconfigurable Computing Systems. Proc. of the IEEE, 90, 7 (2002).

- Buell D., El-Ghazawi T., Gaj K., Kindratenko V., *High-Performance Reconfigurable Computing*. IEEE Comp. Soc., March 2007.

- Cassez F., Roux O.H., Structural Translation from Time Petri Nets to Timed Automata. J. of Syst. a. Software, **79**, 10, 1456-1468 (2006).

- Cristea V., Algoritmi de prelucrare paralelă. Matrix Rom, București, 2002.

- El-Ghazawi T., El-Araby E., Miaoqing Huang, Gaj K., Kindratenko V., Buell D., *The Promise of High-Performance Reconfigurable Computing*. IEEE Comp. Soc., February, 2008, 69 -76.

- Lime D., Roux O.H., *Model Checking of Time Petri Nets Using the State Class Timed Automaton.* J, of Discrete Events Dyn. Syst. Theory a. Appl. (DEDS), **16**, 2, 179-205 (2006).

- Peterson J.L., *Petri Net Theory and the Modeling of Systems*. Prentice-Hall, NY, 1981. Sudacevschi V., *Sinteza structurilor de procesare concurentă a datelor*. Ph. D. Diss., Mold. Techn. Univ., Kishinew, 2009.

- Todman T.J., Constantinides G.A., Wilton S.J.E, Luk W., Cheung P.Y.K., *Reconfigurable Computing: Architectures and Design Methods.* IEEE Proc. of Comp. Dig. Technol., **152**, 2 (2005).

- \* \* http://www.altera.com/, accessed 10.09.2013.

## MODELAREA ȘI SINTEZA SISTEMELOR DE CONTROL ÎN TIMP REAL ÎN BAZA REȚELELOR PETRI HARD TEMPORIZATE

(Rezumat)

Se propune o metodă de sinteză a sistemelor de control în timp real bazată pe maparea directă a modelului rețelei Petri în circuite FPGA. Pentru specificarea și modelarea sistemului de control au fost elaborate rețelele Petri de control sincrone temporizate. Trecerea la descrierea hard a sistemului se realizează prin intermediul rețelelor Petri Hard Temporizate (RPHT). Corespondența directă dintre elementele specificației inițiale și componentele circuitului rezultat asigură respectarea proprietăților comportamentale și a restrângerilor temporale ale sistemului de control.