BULETINUL INSTITUTULUI POLITEHNIC DIN IAȘI Publicat de Universitatea Tehnică "Gheorghe Asachi" din Iași Tomul LX (LXIV), Fasc. 3, 2014 Secția ELECTROTEHNICĂ. ENERGETICĂ. ELECTRONICĂ

# A CMOS CURRENT REFERENCE CIRCUIT WITHOUT RESISTORS

BY

### **DAMIAN IMBREA**<sup>\*</sup>

"Gheorghe Asachi" Technical University of Iaşi Faculty of Electronics, Telecommunications and Information Technology

Received: July 10, 2014 Accepted for publication: July 31, 2014

**Abstract.** A method of obtaining reference currents in CMOS circuits without resistors is presented. The proposed circuit is implemented in 65 nm CMOS standard technology and operates with voltage supply in the range [2.2... 2.8] V from  $-25^{\circ}$ C to  $+130^{\circ}$ C. The reference current is 1  $\mu$ A  $\pm$  1 nA, has a temperature coefficient of 12.9 ppm/°C and a line sensitivity of 8.7 nA/V. The circuit has also a good power supply rejection rate (-164 dB at low frequencies).

**Key words:** current reference; temperature coefficient; line sensitivity; power supply rejection rate.

### 1. Introduction

Most of CMOS current reference circuits are based on summing currents with negative and positive temperature coefficients.

The emitter-base voltage  $V_{EB}$  of bipolar transistors and the difference between two  $V_{EB}$  (the thermal voltage  $V_T$ ) have thermal characteristics that are usually exploited in generating currents with negative and positive temperature gradients;  $V_{EB}$  decreases approximately linear with temperature (-2 mV/°C) while  $V_T$  increases linearly with temperature (+0.085 mV/°C).

The conversion of voltages like  $V_{EB}$  and  $V_T$  into currents can be carried

<sup>\*</sup>*E-mail*: dimbrea@etti.tuiasi.ro

out *via* resistors (Imbrea *et al.*, 2013), *via* MOS transistors operating in triode regime (De Vita *et al.*, 2007) or via active MOS transistors (Imbrea *et al.*, 2013), (Falconi *et al.*, 2007), (Quemada *et al.*, 2012).

The difference between currents with negative temperature coefficients may also produce reference currents (Zhao *et al.*, 2012). Currents having negative temperature gradient are generated in (Liu *et al.*, 2010) by means of the threshold difference between a thin and a thick oxide MOS transistor.

## 2. The Proposed Method to Generate a Reference Current and Circuit Description

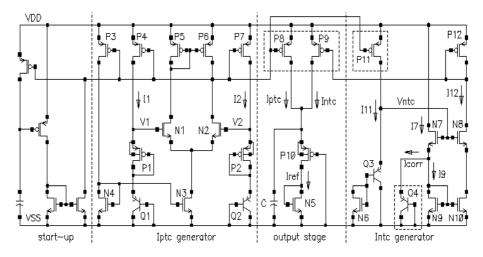

The schematic of the circuit contains four parts as shown in Fig.1, namely start-up,  $I_{ptc}$  generator,  $I_{ntc}$  generator and output stage ( $I_{ptc}$  and  $I_{ntc}$  denote currents having positive and negative temperature coefficient, respectively). The start-up is necessary because  $I_{ptc}$  generator is self-biased. The nominal supply voltage is 2.5 V. The devices  $Q_1$ ,  $Q_2$ ,  $Q_3$  and  $Q_4$  are vertical PNP bipolar transistors. The channels of all MOS transistors are long enough so the length modulation can be ignored.

Fig. 1 – Schematic of the proposed current reference circuit.

The characteristic I-V of a MOS transistor working in the saturation region and strong inversion can be expressed as below

$$I_D = \frac{1}{2} \mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 = \frac{1}{2} K (V_{GS} - V_{TH})^2, \ K = \mu C_{ox} \frac{W}{L},$$

(1)

where  $\mu$  is the mobility of charge carriers in the channel,  $C_{ox}$  – the oxide capacitance per unit area, W and L – the channel sizes and  $V_{TH}$  is the threshold voltage.

The  $I_{ptc}$  generator is similar with that presented in (Imbrea *et al.*, 2013) and consists of a self-biased differential amplifier. No frequency compensation is needed for stability because the phase margin is greater than 60 degrees.

Starting from  $V_1 = V_2$  and  $I_1 = I_2$ , constraints imposed by the amplifier, we obtain the following equations. Both transistors  $P_1$  and  $P_2$  are working in strong inversion

$$V_{SG(P_1)} + V_{EB1} = V_{SG(P_2)} + V_{EB2},$$

(2)

$$V_{TH(P_1)} + \sqrt{\frac{2I_1}{K_{P_1}}} - V_{TH(P_2)} - \sqrt{\frac{2I_2}{K_{P_2}}} = V_T \ln N,$$

(3)

where: *N* represents the ratio between areas of  $Q_1$  and  $Q_2$ . Assuming that  $V_{TH(P_1)}$  and  $V_{TH(P_2)}$  are equal, we obtain

$$\sqrt{I} = \frac{\sqrt{K_{P_1}}\sqrt{K_{P_2}}}{\sqrt{2}\left(\sqrt{K_{P_2}} - \sqrt{K_{P_1}}\right)} V_T \ln N,$$

(4)

where the letter *I* denote the common value of  $I_1$  and  $I_2$ . Obviously,  $K_{P_2}$  must be greater than  $K_{P_1}$ . Eq. (4) may be expressed as

$$I = K_{P}V_{T}^{2}, \quad \sqrt{K_{P}} = \frac{\sqrt{K_{P_{1}}}\sqrt{K_{P_{2}}}\ln N}{\sqrt{2}\left(\sqrt{K_{P_{2}}} - \sqrt{K_{P_{1}}}\right)}.$$

(5)

The term  $K_P V_T$  in eq. (5) is nearly constant with temperature so the current *I* has a positive temperature coefficient, being approximately proportional to the absolute temperature *T*. The current  $I_{ptc}$  injected in the output stage, proportional to *I*, is obtained by choosing a proper width *W* for the transistor P<sub>8</sub>.

The  $I_{ntc}$  generator uses as input a voltage  $V_{ntc}$  with negative temperature coefficient; it is produced by  $P_{11}$ ,  $Q_3$  and  $N_6$ . The current  $I_{11}$  has to be properly adjusted by means of  $P_{11}$  width. The basic equations that describe the  $I_{ntc}$  generator are presented below.

$$\begin{cases} V_{ntc} = V_{GS(N_7)} + V_{GS(N_9)} = V_{TH(N_7)} + \sqrt{\frac{2I_7}{K_{N_7}}} + V_{TH(N_9)} + \sqrt{\frac{2I_9}{K_{N_9}}}, \\ V_{EB4} = V_{GS(N_9)}, \\ I_{Q_4} = I_{corr} \cong I_S \exp \frac{V_{GS(N_9)}}{V_T}, \\ I_9 = I_7 - I_{corr} = I_{12}. \end{cases}$$

(6)

| Damian Ir | nbrea |

|-----------|-------|

|-----------|-------|

where:  $I_{Q_4}$  is a correction current and, for this reason, it is also named  $I_{corr}$ . The term  $I_S$  denotes the saturation current of a bipolar junction.

It is well known that the threshold voltage of all MOS transistors decreases approximately linear with temperature. The input voltage  $V_{ntc}$  also forces  $K_{GS(N_7)}$  and  $K_{GS(N_9)}$  to decrease with temperature. From eq. (6) we derive the following equation

$$\frac{1}{2}K_{N_{\gamma}}(V_{ntc} - V_{GS(N_{9})} - V_{TH(N_{\gamma})})^{2} - I_{S}\exp\frac{V_{GS(N_{9})}}{V_{T}} = \frac{1}{2}K_{N_{9}}(V_{GS(N_{9})} - V_{TH(N_{9})})^{2} = I_{12}.$$

(7)

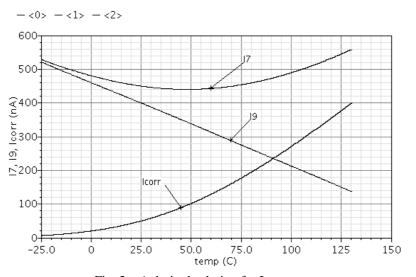

Solving eq. (7) analitically, in order to get a linear decrease with temperature for the current  $I_{12}$ , is a very difficult task. However, we can find the proper sizes of the transistors  $P_{11}$ ,  $N_7$ ,  $N_9$  and  $Q_4$  by simulations ( $P_{11}$  helps produce the required input voltage  $V_{ntc}$ ). Note that  $N_8$  and  $N_{10}$  have the same sizes as  $N_7$  and  $N_9$ , respectively. One solution for eq. (7), based on simulations, is shown in Fig. 2.

Fig. 2 – A desired solution for  $I_{\text{ntc}}$  generator.

The current  $I_{ntc}$  injected in the output stage is proportional to  $I_{12}$  and it is obtained by choosing a proper width W for the transistor P<sub>9</sub>. The output stage implements the equation

$$I_{ref} = I_{ptc} + I_{ntc}.$$

(8)

The capacitor C (about 4 pF) and the active transistor  $P_8$  form together a filter that improves the power supply rejection rate at high frequencies.

#### 3. Simulation Results

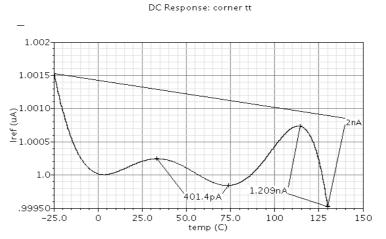

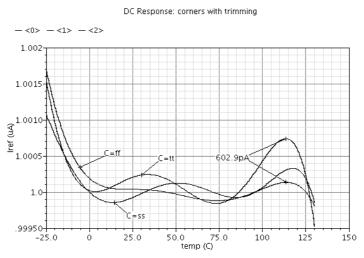

The DC response corresponding to typical corner and 2.5 V supply voltage is illustrated in Fig. 3. The circuit generates a reference current  $I_{ref}$  very close to 1  $\mu$ A. The temperature coefficient (TC) of  $I_{ref}$  is 12.9 ppm/°C in the range [-25...+130]°C. Note that TC drops to half (6.5 ppm/°C) in the temperature range [-18...+128]°C.

Fig. 3 – Influence of temperature on the reference current.

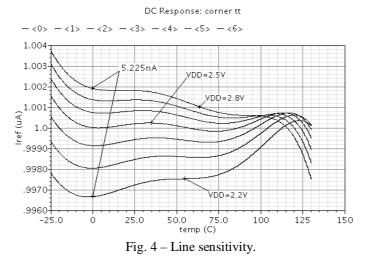

The influence of the supply voltage  $V_{DD}$  on  $I_{ref}$  (also called *line* sensitivity) is shown in Fig. 4. If  $V_{DD}$  changes between 2.2 V and 2.8 V, which means 2.5 V  $\pm$  12%, then  $I_{ref}$  has maximum deviations of -3.2 nA and +2 nA from the nominal values. This means a line sensitivity of about 8.7 nA/V.

Technological process variations affect significantly the current  $I_{ref}$ . At low temperatures the values of  $I_{ref}$  vary much from the typical ones (-28% in slow-slow corner and +43% in fast-fast corner). Also, TC greatly increases. However, the process variations can be compensated by trimming the sizes of transistors marked in Fig. 1 with dashed rectangles, namely P<sub>8</sub>, P<sub>9</sub>, P<sub>11</sub> and Q<sub>4</sub>. The result is presented in Fig. 5. After adjusting the width of P<sub>8</sub>, P<sub>9</sub>, P<sub>11</sub> and the multiplicity factor of Q<sub>4</sub> the two extreme corners, ss and ff, move very close to the typical one.

Fig. 5 – Compensation of process variations by trimming.

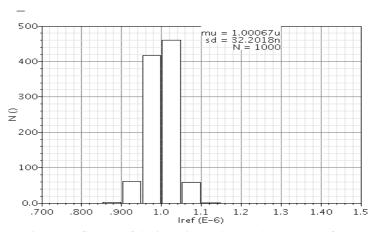

The mismatch between transistors also affects the current  $I_{ref}$ . Monte Carlo simulations are shown in Fig. 6. Some correlations between transistors were considered. The ratio *standard deviation/mean* (sd/mu) of  $I_{ref}$  is 3.23%. Monte Carlo (mismatch): corner tt, VDD=2.5V, temp=27C

Fig. 6 – Influence of device mismatches on the current reference.

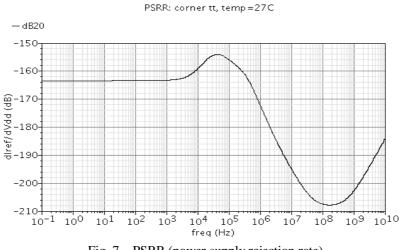

The rejection of the supply voltage is illustrated in Fig.7. At low frequencies the value of PSRR is about -164 dB; it gives the line sensitivity shown in Fig. 4. PSRR decreases below -180 dB at frequencies more than 1 MHz due to the filter  $P_{10} - C$  inserted in the output stage.

Fig. 7 – PSRR (power supply rejection rate).

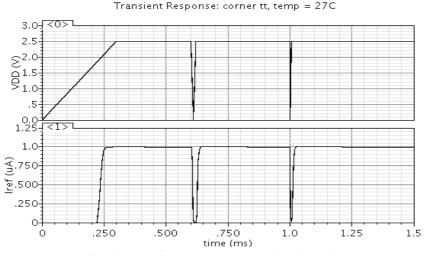

The behavior of the circuit in Fig. 1 to certain supply voltage drops is illustrated in Fig. 8. This transient response shows indirectly a high phase margin of the amplifier from inside the  $I_{ptc}$  generator. The start-up stage is very efficient; it forces the differential amplifier to enter quickly the nominal operating regime, without oscillations or overshoots.

Fig. 8 – Transient response to supply voltage drops.

## 4. Comparisons with Similar Works

Comparisons between this work and those ones referenced in this paper are listed in the Table 1. The abbreviations "NT" and "T" stand for "no trimming" and "trimming", respectively; the abbreviations "std" and "SOI" are used for "standard" and "silicon on insulator", respectively.

The performances of the current reference described in this paper are comparable with those presented in (Imbrea *et al.*, 2013) and are superior to those presented in the other references. In order to decrease the line sensitivity of the proposed circuit it is mandatory to improve PSRR at low frequencies. This parameter is mainly determined by  $I_{ptc}$  and  $I_{ntc}$  generators.

When comparing values of line sensitivity (row 5 in the table 1), we have to take also into account the values of reference current. For example, one may say in case of this work that the voltage supply variation involves a change of 0.87%/V in the output current  $I_{ref}$ .

| Comparisons             |                               |                                |                                |                                 |

|-------------------------|-------------------------------|--------------------------------|--------------------------------|---------------------------------|

|                         | This work                     | Imbrea <i>et al.</i> ,<br>2013 | De Vita <i>et al.,</i><br>2007 | Falconi <i>et al.</i> ,<br>2007 |

| Process                 | 65 nm<br>CMOS<br>std.         | 65 nm<br>CMOS<br>std.          | 0.35 μm<br>CMOS<br>std.        | 0.13 μm<br>CMOS<br>std.         |

| Supply voltage          | [2.2, 2.8] V<br>2.5 V nominal | [2.1, 3.0] V<br>2.5 V nominal  | [2.0, 4.0] V<br>3.0 V nominal  | [0.8, 2.0] V<br>1.5 V nominal   |

| Reference<br>current    | 1 μΑ                          | 1 μΑ                           | 9.14 nA                        | 10 µA                           |

| Line<br>sensitivity     | 8.7 nA/V                      | 0.5 nA/V                       | 5.6 pA/V                       | -                               |

| Temperature coefficient | 12.9 ppm/°C                   | 11 ppm/⁰C                      | 44 ppm/⁰C                      | 2.2 %/°C                        |

| Temperature<br>range    | [-25, +130]<br>°C             | [-40, +130]<br>°C              | [0, +80]<br>°C                 | [-10, +80]<br>°C                |

| Process<br>sensitivity  | Simulated                     | Simulated                      | Measured                       | Simulated                       |

| – mismatch<br>(sd/mu)   | 3.23%                         | 1.53%                          | _                              | -                               |

| - corners               | 43% (NT)<br>0.06% (T)         | 30% (NT)<br>0.036% (T)         | _                              | _                               |

| – total                 | -                             | _                              | 2.16% (NT)                     | 31% (NT)                        |

| PSRR<br>@100Hz          | -164 dB                       | -200 dB                        | _                              | _                               |

Table 1

| Table 1                 |                               |                                        |                              |                               |  |

|-------------------------|-------------------------------|----------------------------------------|------------------------------|-------------------------------|--|

| Comparisons (continued) |                               |                                        |                              |                               |  |

|                         | This work                     | Quemada <i>et</i><br><i>al.</i> , 2012 | Zhao <i>et al.</i> ,<br>2012 | Liu <i>et al.</i> ,<br>2010   |  |

| Process                 | 65 nm<br>CMOS<br>std.         | 0.18 μm<br>CMOS<br>SOI                 | 0.18 μm<br>CMOS<br>std.      | 0.18 μm<br>CMOS<br>std.       |  |

| Supply<br>voltage       | [2.2, 2.8] V<br>2.5 V nominal | –<br>1.5 V nominal                     | –<br>1.8 V nominal           | [2.0, 3.0] V<br>2.0 V nominal |  |

| Reference<br>current    | 1 μΑ                          | 21.1 µA                                | 4.2 μΑ                       | 10 µA                         |  |

| Line<br>sensitivity     | 8.7 nA/V                      | _                                      | _                            | 0.3 µA/V                      |  |

| Temperature coefficient | 12.9 ppm/°C                   | 16.5 ppm/°C                            | 273 ppm/°C                   | 170 ppm/°C                    |  |

| Temperature<br>range    | [-25, +130]<br>°C             | [+20, +130]<br>°C                      | [-10, +100]<br>°C            | [-20, +120]<br>°C             |  |

| Process<br>sensitivity  | Simulated                     | Simulated                              | Simulated                    | Simulated                     |  |

| – mismatch<br>(sd/mu)   | 3.23%                         | _                                      | _                            | _                             |  |

| - corners               | 43% (NT)<br>0.06% (T)         | 38% (NT)                               | 33% (NT)                     | _                             |  |

| – total                 | -                             | —                                      | _                            | 2.14% (NT)                    |  |

| PSRR<br>@100Hz          | -164 dB                       | _                                      | -                            | -                             |  |

# Table 1

### **5.** Conclusions

The current reference described in this work is built only with regular MOS transistors and vertical substrate PNP transistors; no on-chip resistors or external components are used. The circuit is designed in 65 nm CMOS standard process but can be implemented in any other one. The process variations and device mismatches can be compensated by trimming the sizes of four transistors. Simulations show that the generated current of 1  $\mu$ A is very weakly sensitive to temperature and voltage supply variations.

### REFERENCES

- De Vita G., Iannaccone G., A 109 nW, 49 ppm/°C CMOS Current Reference with Low Sensitivity to Process Variations. ISCAS, 3804-3807 (2007).

- Falconi C., et al., Low Voltage CMOS Current and Voltage References Without Resistors. ISCAS, 1907-1910 (2007).

- Imbrea D., Cojan N., A 11 ppm/°C CMOS Current Reference Circuit with no External Components. ISSCS, 40-43 (2013).

| D            |       |      | 1    |

|--------------|-------|------|------|

| 1)2          | ımian | Im   | hrea |

| $-\nu \iota$ | uman  | 1111 | orca |

Liu W., et al., A Resistor-Free Temperature-Compensated CMOS Current Reference. ISCAS, 845-848 (2010).

Quemada C., Cochran T. L., Sam Ha D., A Compact Resistorless 1.5-V CMOS Current Reference with 16.5-ppm/°C Temperature Coefficient. ISCAS, 3146-3149 (2012).

Zhao C., Geiger R., Chen D., A Compact Low-Power Supply-Insensitive CMOS Current Reference. ISCAS, 2825-2828 (2012).

### REFERINȚĂ DE CURENT CMOS FĂRĂ REZISTORI

### (Rezumat)

Se prezintă un circuit CMOS fără rezistori, care generează un curent de referință cu valoarea 1  $\mu$ A ± 1 nA în gama de temperatură [-25°, +130]°C. Curentul de referință se obține prin sumarea a doi curenți care au coeficienți de temperatură pozitiv și respectiv negativ. Tensiunea de alimentare este 2.5 V ± 12%.

Caracteristicile principale ale referinței de curent propuse sunt coeficientul de temperatură 12.9 ppm/°C, sensibilitatea 8.7 nA/V la tensiunea de alimentare și rejecția variațiilor de pe linia de alimentare de –164 dB la frecvențe mici.

Influența variațiilor procesului tehnologic asupra curentului de referință pot fi compensate prin ajustarea dimensiunilor a patru tranzistoare. Simulările de tip Monte Carlo arată o dispersie de 32.2 nA a curentului de referință datorită neîmperechierilor dintre tranzistoare.